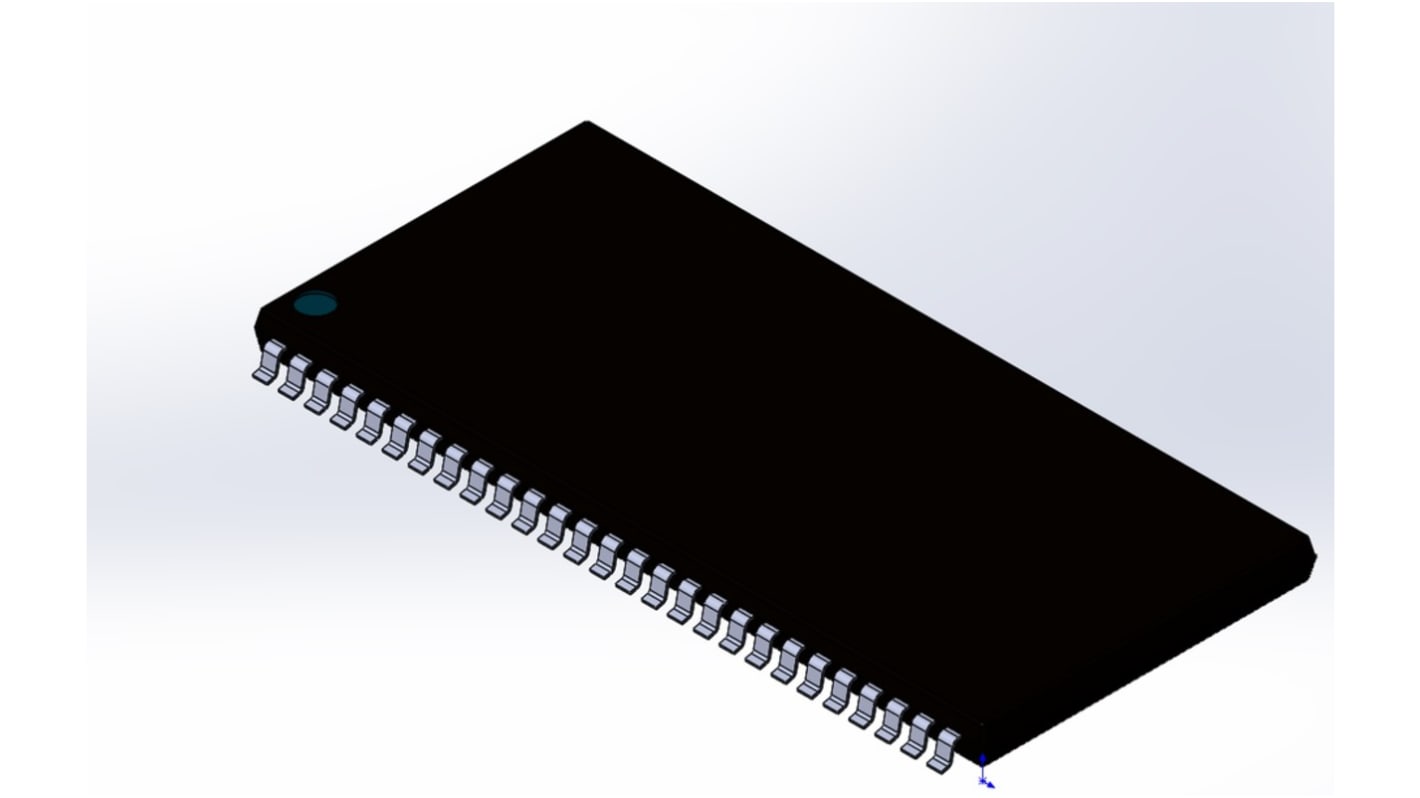

Alliance Memory AS4C4M16SA-7TCN SDRAM 64 MB Surface, 54-Pin 16 bit TSOP

- N° de stock RS:

- 230-8434

- Référence fabricant:

- AS4C4M16SA-7TCN

- Fabricant:

- Alliance Memory

Offre groupée disponible

Sous-total (1 paquet de 5 unités)*

11,58 €

(TVA exclue)

14,01 €

(TVA incluse)

Informations sur le stock actuellement non accessibles - Veuillez vérifier plus tard

Unité | Prix par unité | le paquet* |

|---|---|---|

| 5 - 5 | 2,316 € | 11,58 € |

| 10 - 20 | 2,092 € | 10,46 € |

| 25 - 45 | 2,054 € | 10,27 € |

| 50 - 70 | 2,044 € | 10,22 € |

| 75 + | 2,002 € | 10,01 € |

*Prix donné à titre indicatif

- N° de stock RS:

- 230-8434

- Référence fabricant:

- AS4C4M16SA-7TCN

- Fabricant:

- Alliance Memory

Spécifications

Documentation technique

Législations et de normes

Détails du produit

Recherchez des produits similaires en sélectionnant un ou plusieurs attributs.

Sélectionner tout | Attribut | Valeur |

|---|---|---|

| Marque | Alliance Memory | |

| Memory Size | 64MB | |

| Product Type | SDRAM | |

| Data Bus Width | 16bit | |

| Address Bus Width | 12bit | |

| Maximum Clock Frequency | 166MHz | |

| Number of Bits per Word | 16 | |

| Maximum Random Access Time | 5.4ns | |

| Number of Words | 1M | |

| Mount Type | Surface | |

| Package Type | TSOP | |

| Pin Count | 54 | |

| Minimum Operating Temperature | 0°C | |

| Maximum Operating Temperature | 70°C | |

| Series | AS4C4M16SA-C&I | |

| Height | 1.2mm | |

| Length | 22.35mm | |

| Standards/Approvals | No | |

| Automotive Standard | No | |

| Minimum Supply Voltage | 3V | |

| Maximum Supply Voltage | 3.6V | |

| Sélectionner tout | ||

|---|---|---|

Marque Alliance Memory | ||

Memory Size 64MB | ||

Product Type SDRAM | ||

Data Bus Width 16bit | ||

Address Bus Width 12bit | ||

Maximum Clock Frequency 166MHz | ||

Number of Bits per Word 16 | ||

Maximum Random Access Time 5.4ns | ||

Number of Words 1M | ||

Mount Type Surface | ||

Package Type TSOP | ||

Pin Count 54 | ||

Minimum Operating Temperature 0°C | ||

Maximum Operating Temperature 70°C | ||

Series AS4C4M16SA-C&I | ||

Height 1.2mm | ||

Length 22.35mm | ||

Standards/Approvals No | ||

Automotive Standard No | ||

Minimum Supply Voltage 3V | ||

Maximum Supply Voltage 3.6V | ||

The Alliance Memory 64Mb SDRAM is a high-speed CMOS synchronous DRAM containing 64 Mbits. It is internally configured as 4 Banks of 1M word x 16 DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Read and write accesses to the SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of a Bank Activate command which is then followed by a Read or Write command.

Fast access time from clock: 4.5/5.4/5.4 ns

Fast clock rate: 200/166/143 MHz

Fully synchronous operation

Internal pipelined architecture

1M word x 16-bit x 4-bank

Liens connexes

- Alliance Memory SDRAM 64 MB Surface, 54-Pin 16 bit TSOP

- Alliance Memory AS4C4M16SA-6TIN SDRAM 64 MB Surface, 54-Pin 16 bit TSOP

- Alliance Memory AS4C8M16SA-7TCN SDRAM 128 MB Surface, 54-Pin 16 bit TSOP

- Alliance Memory AS4C16M16SA-7TCN SDRAM 256 MB Surface, 54-Pin 16 bit TSOP

- Alliance Memory AS4C32M16SB-7TCN SDRAM 512 MB Surface, 54-Pin 16 bit TSOP

- Alliance Memory SDRAM 128 MB Surface, 54-Pin 16 bit TSOP

- Alliance Memory SDRAM 512 MB Surface, 54-Pin 16 bit TSOP

- Alliance Memory SDRAM 256 MB Surface, 54-Pin 16 bit TSOP