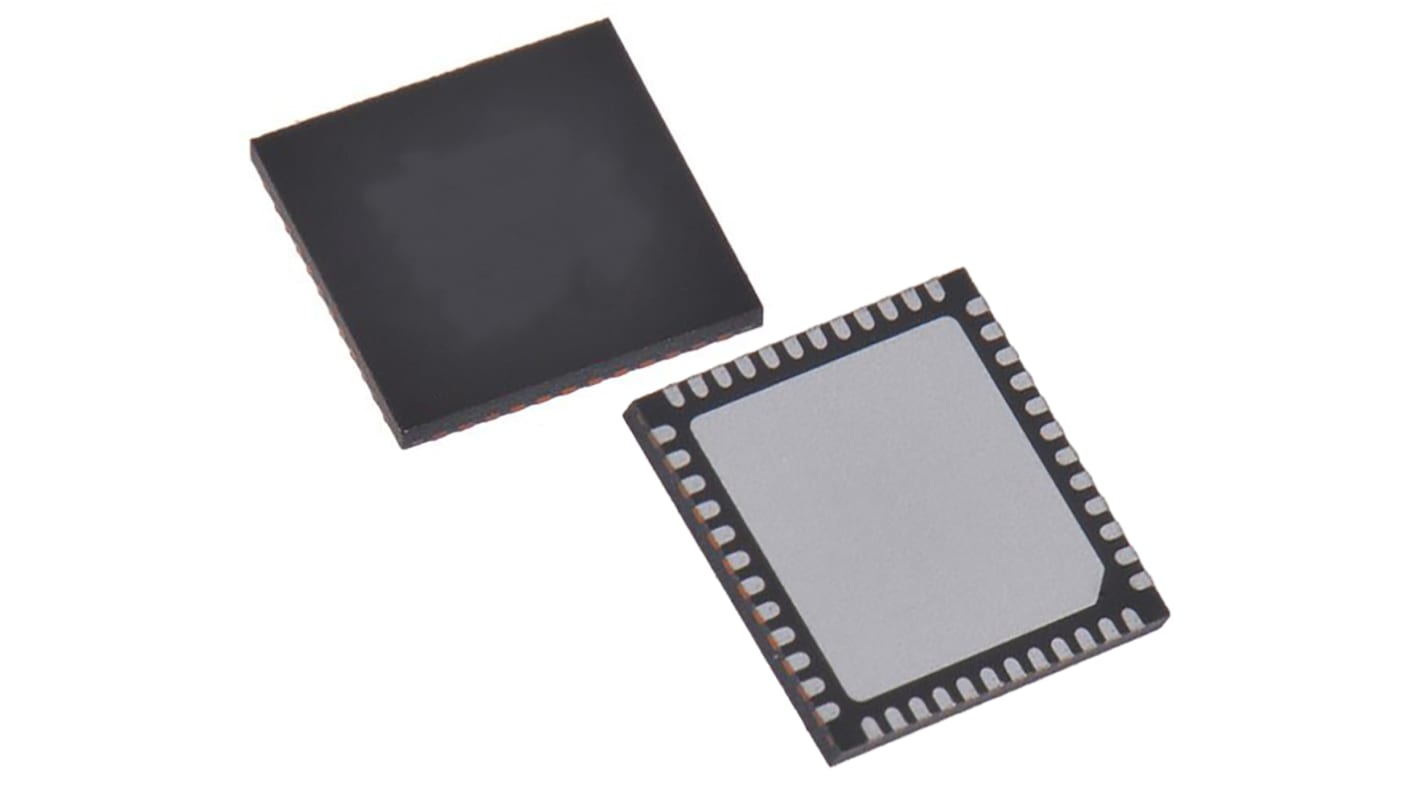

STMicroelectronics STM32WB55CEU6 CMOS Wireless System On Chip SOC 48-Pin UFQFPN

- N° de stock RS:

- 192-3955

- Référence fabricant:

- STM32WB55CEU6

- Fabricant:

- STMicroelectronics

Offre groupée disponible

Sous-total (1 paquet de 2 unités)*

11,69 €

(TVA exclue)

14,144 €

(TVA incluse)

Frais de livraison offerts pour toute commande de plus de 80,00 €

Temporairement en rupture de stock

- Expédition à partir du 12 novembre 2026

Besoin de plus? Cliquez sur " Vérifier les dates de livraison " pour plus de détails

Unité | Prix par unité | le paquet* |

|---|---|---|

| 2 - 8 | 5,845 € | 11,69 € |

| 10 - 18 | 5,495 € | 10,99 € |

| 20 - 48 | 5,195 € | 10,39 € |

| 50 - 98 | 4,91 € | 9,82 € |

| 100 + | 4,67 € | 9,34 € |

*Prix donné à titre indicatif

- N° de stock RS:

- 192-3955

- Référence fabricant:

- STM32WB55CEU6

- Fabricant:

- STMicroelectronics

Spécifications

Documentation technique

Législations et de normes

Détails du produit

Recherchez des produits similaires en sélectionnant un ou plusieurs attributs.

Sélectionner tout | Attribut | Valeur |

|---|---|---|

| Marque | STMicroelectronics | |

| Processing Unit | Bluetooth | |

| Product Type | Wireless System On Chip SOC | |

| Technology | CMOS | |

| Mount Type | Surface | |

| Package Type | UFQFPN | |

| Pin Count | 48 | |

| Clock Frequency | 64MHz | |

| Program Memory Size | 512kB | |

| Interface Type | SPI | |

| Program Memory Type | FLASH | |

| Minimum Supply Voltage | 1.71V | |

| Maximum Supply Voltage | 3.6V | |

| Data RAM Type | SRAM | |

| Minimum Operating Temperature | -40°C | |

| Number of I/Os | 72 | |

| Data RAM Size | 256kB | |

| Maximum Operating Temperature | 85°C | |

| Standards/Approvals | No | |

| Series | STM32WB | |

| Width | 7.1 mm | |

| Height | 0.55mm | |

| Length | 7.1mm | |

| Automotive Standard | No | |

| Sélectionner tout | ||

|---|---|---|

Marque STMicroelectronics | ||

Processing Unit Bluetooth | ||

Product Type Wireless System On Chip SOC | ||

Technology CMOS | ||

Mount Type Surface | ||

Package Type UFQFPN | ||

Pin Count 48 | ||

Clock Frequency 64MHz | ||

Program Memory Size 512kB | ||

Interface Type SPI | ||

Program Memory Type FLASH | ||

Minimum Supply Voltage 1.71V | ||

Maximum Supply Voltage 3.6V | ||

Data RAM Type SRAM | ||

Minimum Operating Temperature -40°C | ||

Number of I/Os 72 | ||

Data RAM Size 256kB | ||

Maximum Operating Temperature 85°C | ||

Standards/Approvals No | ||

Series STM32WB | ||

Width 7.1 mm | ||

Height 0.55mm | ||

Length 7.1mm | ||

Automotive Standard No | ||

- Pays d'origine :

- CN

Wireless and ultra-low-power devices embed a powerful and ultra-low-power radio. They contain a dedicated Arm® Cortex® -M0+ for performing all the real-time low layer operation.

Designed to be extremely low-power and are based on the high-performance Arm® Cortex®-M4 32-bit RISC core operating at a frequency of up to 64 MHz. The Cortex®-M4 core features a Floating point unit (FPU) single precision that supports all Arm® single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) that enhances application security.

Enhanced inter-processor communication is provided by the IPCC with six bidirectional channels. The HSEM provides hardware semaphores used to share common resources between the two processors.

High-speed memories (Flash memory up to 1 Mbyte, up to 256 Kbyte of SRAM), a Quad-SPI Flash memory interface (available on all packages) and an extensive range of enhanced I/Os and peripherals.

Liens connexes

- STMicroelectronics CMOS Wireless System On Chip SOC 48-Pin UFQFPN

- STMicroelectronics CMOS Wireless System On Chip SOC 68-Pin VFQFPN

- STMicroelectronics STM32WB55RGV6 CMOS Wireless System On Chip SOC 68-Pin VFQFPN

- Texas Instruments CC8530RHAT Wireless Headphone

- Texas Instruments CC8520RHAT Wireless Headphone

- onsemi AX-SFEU-API-1-01-TB05, CMOS/TTL Wireless System On Chip SOC 40-Pin QFN

- Infineon CMOS System On Chip SOC 28-Pin SSOP

- Infineon CMOS System On Chip SOC 100-Pin TQFP