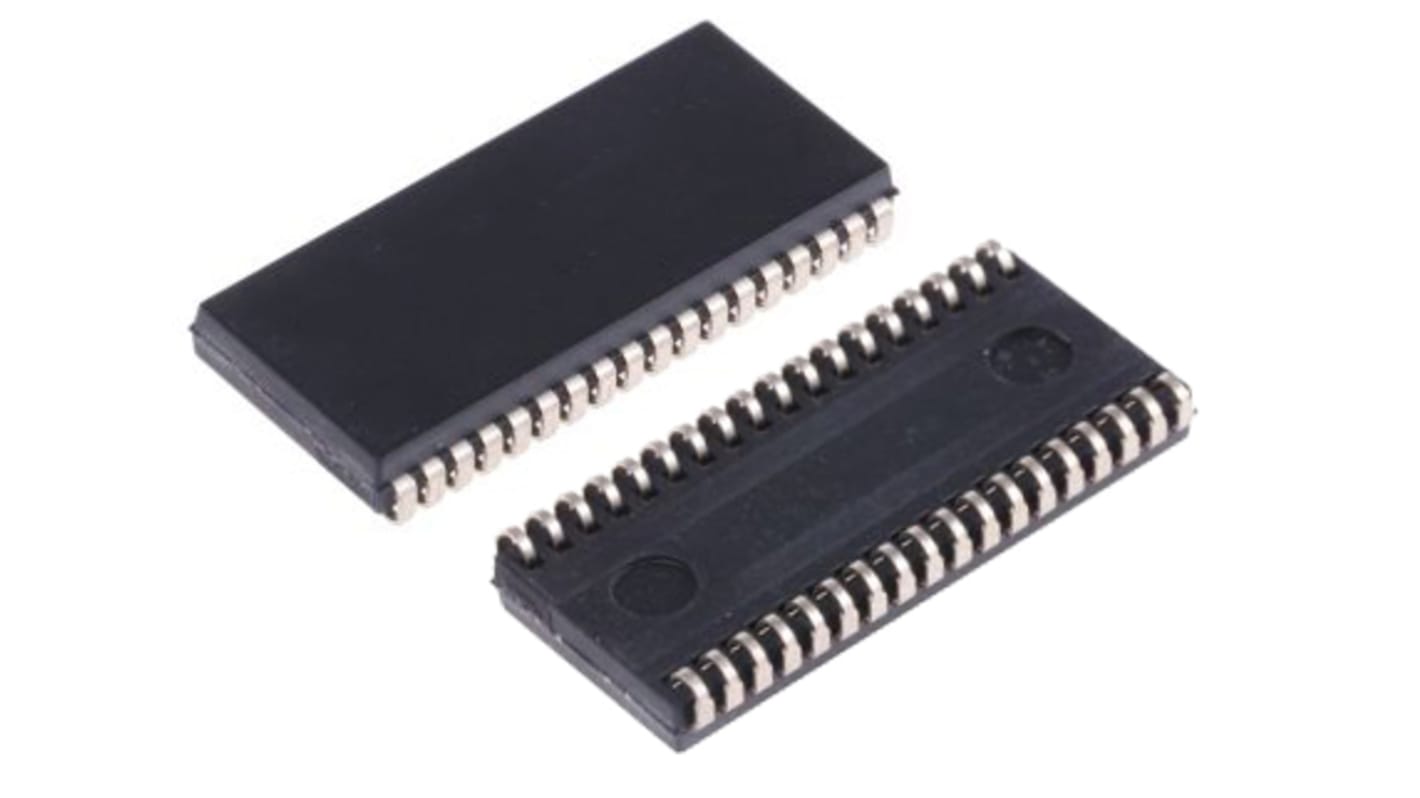

Infineon SRAM Memory Chip, CY7C1049G30-10VXI- 4Mbit

- N° de stock RS:

- 193-8466

- Référence fabricant:

- CY7C1049G30-10VXI

- Fabricant:

- Infineon

Indisponible

RS n'aura plus ce produit en stock.

- N° de stock RS:

- 193-8466

- Référence fabricant:

- CY7C1049G30-10VXI

- Fabricant:

- Infineon

Spécifications

Documentation technique

Législations et de normes

Détails du produit

Recherchez des produits similaires en sélectionnant un ou plusieurs attributs.

Sélectionner tout | Attribut | Valeur |

|---|---|---|

| Marque | Infineon | |

| Memory Size | 4Mbit | |

| Organisation | 512k x 8 bit | |

| Number of Words | 512k | |

| Number of Bits per Word | 8bit | |

| Maximum Random Access Time | 10ns | |

| Address Bus Width | 8bit | |

| Clock Frequency | 100MHz | |

| Timing Type | Asynchronous | |

| Mounting Type | Through Hole | |

| Package Type | SOJ | |

| Pin Count | 36 | |

| Dimensions | 0.92 x 0.395 x 0.103in | |

| Maximum Operating Supply Voltage | 3.6 V | |

| Height | 2.62mm | |

| Width | 10.03mm | |

| Minimum Operating Temperature | -40 °C | |

| Minimum Operating Supply Voltage | 2.2 V | |

| Maximum Operating Temperature | +85 °C | |

| Length | 23.37mm | |

| Sélectionner tout | ||

|---|---|---|

Marque Infineon | ||

Memory Size 4Mbit | ||

Organisation 512k x 8 bit | ||

Number of Words 512k | ||

Number of Bits per Word 8bit | ||

Maximum Random Access Time 10ns | ||

Address Bus Width 8bit | ||

Clock Frequency 100MHz | ||

Timing Type Asynchronous | ||

Mounting Type Through Hole | ||

Package Type SOJ | ||

Pin Count 36 | ||

Dimensions 0.92 x 0.395 x 0.103in | ||

Maximum Operating Supply Voltage 3.6 V | ||

Height 2.62mm | ||

Width 10.03mm | ||

Minimum Operating Temperature -40 °C | ||

Minimum Operating Supply Voltage 2.2 V | ||

Maximum Operating Temperature +85 °C | ||

Length 23.37mm | ||

CY7C1049G and CY7C1049GE are high-performance CMOS fast static RAM devices with embedded ECC. Both devices are offered in single and dual chip-enable options and in multiple pin configurations. The CY7C1049GE device includes an ERR pin that signals an error-detection and correction event during a read cycle. Data writes are performed by asserting the Chip Enable (CE) and Write Enable (WE) inputs LOW, while providing the data on I/O0through I/O7 and address on A0 through A18 pins. Data reads are performed by asserting the Chip Enable (CE) and Output Enable (OE) inputs LOW and providing the required address on the address lines. Read data is accessible on the I/O lines (I/O0 through I/O7).

High speed

tAA = 10 ns

Embedded ECC for single-bit error correction[1, 2]

Low active and standby currents

Active current: ICC = 38 mA typical

Standby current: ISB2 = 6 mA typical

Operating voltage range: 1.65 V to 2.2 V, 2.2 V to 3.6 V, and4.5 V to 5.5 V

1.0-V data retention

TTL-compatible inputs and outputs

Error indication (ERR) pin to indicate 1-bit error detection and correction

Pb-free 36-pin SOJ and 44-pin TSOP II packages

tAA = 10 ns

Embedded ECC for single-bit error correction[1, 2]

Low active and standby currents

Active current: ICC = 38 mA typical

Standby current: ISB2 = 6 mA typical

Operating voltage range: 1.65 V to 2.2 V, 2.2 V to 3.6 V, and4.5 V to 5.5 V

1.0-V data retention

TTL-compatible inputs and outputs

Error indication (ERR) pin to indicate 1-bit error detection and correction

Pb-free 36-pin SOJ and 44-pin TSOP II packages

Liens connexes

- Infineon SRAM Memory Chip, CY7C1049G30-10VXI- 4Mbit

- Infineon SRAM, CY7C1049G30-10VXI- 4 MB

- Infineon SRAM Memory Chip, CY7C1018DV33-10VXI- 1Mbit

- Infineon SRAM- 4 MB

- Infineon SRAM Memory Chip, CY7C1021D-10VXIT- 1Mbit

- Infineon SRAM Memory Chip, CY7C1021DV33-10VXIT- 1Mbit

- Infineon SRAM, CY7C1049G30-10ZSXI- 4 MB

- Alliance Memory SRAM, AS6C4008-55TIN- 4Mbit