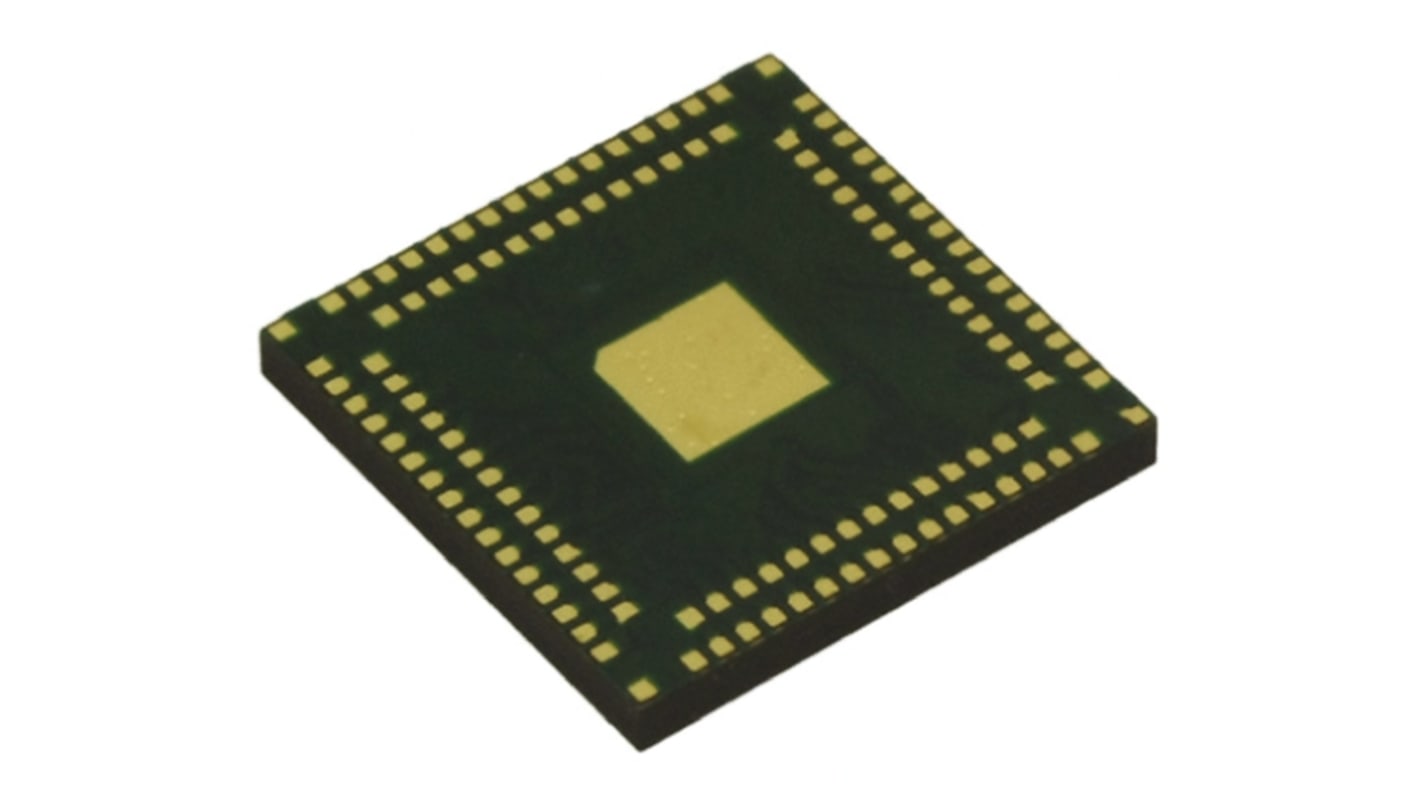

XMOS Multi-Core, XS1 Microcontroller, 60 MHz, 128kB FLASH, 124-Pin QFN

- N° de stock RS:

- 170-0886

- Référence fabricant:

- XS1-L02A-QF124-C5

- Fabricant:

- XMOS

Sous-total (1 plateau de 168 unités)*

4 967,424 €

(TVA exclue)

6 010,536 €

(TVA incluse)

Informations sur le stock actuellement non accessibles - Veuillez vérifier plus tard

Unité | Prix par unité | le plateau* |

|---|---|---|

| 168 + | 29,568 € | 4 967,42 € |

*Prix donné à titre indicatif

- N° de stock RS:

- 170-0886

- Référence fabricant:

- XS1-L02A-QF124-C5

- Fabricant:

- XMOS

Spécifications

Documentation technique

Législations et de normes

Détails du produit

Recherchez des produits similaires en sélectionnant un ou plusieurs attributs.

Sélectionner tout | Attribut | Valeur |

|---|---|---|

| Marque | XMOS | |

| Product Type | Microcontroller | |

| Series | XS1 | |

| Package Type | QFN | |

| Mount Type | Surface | |

| Pin Count | 124 | |

| Device Core | Multi-Core | |

| Program Memory Size | 128kB | |

| Interface Type | JTAG, SPI | |

| Maximum Clock Frequency | 60MHz | |

| RAM Size | 128kB | |

| Maximum Supply Voltage | 3.6V | |

| Number of Programmable I/Os | 84 | |

| Maximum Power Dissipation Pd | 450W | |

| Minimum Operating Temperature | -40°C | |

| Maximum Operating Temperature | 85°C | |

| Standards/Approvals | REACH, RoHS3 | |

| Length | 10mm | |

| Height | 1.11mm | |

| Minimum Supply Voltage | 3V | |

| Automotive Standard | No | |

| Program Memory Type | FLASH | |

| Instruction Set Architecture | RISC | |

| Sélectionner tout | ||

|---|---|---|

Marque XMOS | ||

Product Type Microcontroller | ||

Series XS1 | ||

Package Type QFN | ||

Mount Type Surface | ||

Pin Count 124 | ||

Device Core Multi-Core | ||

Program Memory Size 128kB | ||

Interface Type JTAG, SPI | ||

Maximum Clock Frequency 60MHz | ||

RAM Size 128kB | ||

Maximum Supply Voltage 3.6V | ||

Number of Programmable I/Os 84 | ||

Maximum Power Dissipation Pd 450W | ||

Minimum Operating Temperature -40°C | ||

Maximum Operating Temperature 85°C | ||

Standards/Approvals REACH, RoHS3 | ||

Length 10mm | ||

Height 1.11mm | ||

Minimum Supply Voltage 3V | ||

Automotive Standard No | ||

Program Memory Type FLASH | ||

Instruction Set Architecture RISC | ||

- Pays d'origine :

- SG

XS1 Event-Driven Processor

An XS1 combines a number of XCore™ processors, each with its own memory, on a single chip. The programmable processors are general purpose in the sense that they can execute languages such as C; they also have direct support for concurrent processing (multi-threading), communication and input-output. A high-performance switch supports communication between the processors, and inter-chip XMOS Links are provided so that systems can easily be constructed from multiple chips. The XS1 products are intended to make it practical to use software to perform many functions which would normally be done by hardware; an important example is interfacing and input-output controllers.

Each XCore processor provides the following resources:

32-bit processor providing up to 500MIPS

Eight hardware threads and 32 channel ends

Ten timers and six clock blocks

Four XMOS Links

64KBytes SRAM and 8KBytes OTP memory

The XCore is a multithreaded processing component with instruction set support for communication, input-output and timing. Thread execution is deterministic and the time taken to execute a sequence of instructions can be accurately predicted. This makes it possible for software executing on an XCore to perform many functions normally performed by hardware, especially DSP and I/O.,Each XCore thread has a dedicated set of registers and scheduling of threads is performed by hardware. Communication between threads is performed using hardware channels. Communication instructions transfer data directly between processor registers and channels, automatically scheduling and descheduling the communicating threads to control the flow of data.,The XCore has an efficient set of instructions to support conventional sequential programming languages. Its multithreading, communication and input-output instructions are designed to support modern concurrent programming languages. The instruction set is easily extensible to provide applications-specific instructions; these currently include support for long-arithmetic, CRC, DSP and cryptography.,Each XCore has a single unified memory system which is shared for program and data by all of the threads executed by the core. Multiple threads can share the same program in memory and can pass ownership of data between them. No caches are used.,The XCore has a tightly integrated set of I/O ports controlled directly by instructions. Data is transferred directly between processor registers and ports, avoiding the use of memory and minimizing latency. The ports can serialize and deserialize data enabling the processor to handle high speed data streams. They can also timestamp data arrival, and accurately control the time at which data is transferred to or from the pins.

Liens connexes

- XMOS XS1-L02A-QF124-C5 Multi-Core 60 MHz 124-Pin QFN

- XMOS XS1-L01A-TQ128-C5 Multi-Core 60 MHz FLASH, 128-Pin TQFP

- XMOS Microcontroller MCU

- Microchip PIC 128kB FLASH, 64-Pin QFN

- Microchip PIC 128kB FLASH, 28-Pin QFN

- Microchip PIC18F67K22-E/MR PIC 128kB FLASH, 64-Pin QFN

- Microchip PIC18F27K40-E/ML PIC 128kB FLASH, 28-Pin QFN

- Microchip PIC18F27K40T-I/ML PIC 128kB FLASH, 28-Pin QFN